# High Current TLP Characterisation: An Effective Tool for the Development of Semiconductor Devices and ESD Protection Solutions

Werner Simbürger, David Johnsson, Matthias Stecher High Power Pulse Instruments (HPPI) GmbH, Stadlerstrasse 6A, D-85540 Haar, Germany E-mail: werner.simbuerger@hppi.de, Phone: +49 89 8780698 - 442, Internet: http://www.hppi.de

Abstract—The classical Transmission Line Pulse (TLP) measurement system consists of a 50  $\Omega$  high voltage pulse generator, a high speed digital oscilloscope, a Source Meter Unit (SMU) and a control computer. The typical range of the pulse waveform parameters are: output voltage amplitude in the range of up to  $\pm 4~\rm kV$ , output currents up to  $\pm 80~\rm A$ , pulse width in the range of 1 ns up to 1.6  $\rm \mu s$ , pulse rise time in the range from 100 ps to 50 ns. The transient voltage and currents in the device under test (DUT) are recorded using a high speed digital oscilloscope with e.g. 12 GHz bandwidth and 40 GS/s sampling rate.

Such a measurement system can be used very effective to investigate transient characteristics of semiconductor devices and circuits in the high voltage and high current time domain.

This paper gives an introduction about the basic principle of a high voltage TLP generator and how it can be used effectively for device characterisation and electrostatic discharge (ESD) design.

## I. Introduction

The characterisation of devices and circuits in pulsed mode has two major advantages: a) diminish self heating effects and b) limit the dissipated energy in the device in order to avoid destruction. Usually the pulsed mode is helpful to investigate specific device or circuit parameters in the time domain, such as:

- High current I-V characteristics

- Turn-on/off transient characteristics

- · Breakdown effects

- Charge recovery effects e.g. reverse and forward recovery of diodes

- Safe Operating Area (SOA) or Wunsch-Bell characteristics

- Ruggedness of transistors (RF-LDMOS, DMOS, CMOS, BJT, ...)

- · MOS gate oxide reliability

- Packaging and handling ESD, published in the joint standard ANSI/ESDA/JEDEC JS-001-2010

- Human-Metal-Model (HMM) and system level ESD (IEC-61000-4-2)

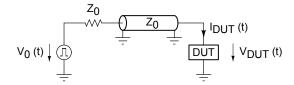

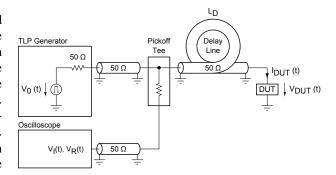

If the pulse width and pulse rise time becomes small, impedance matched transmission lines are used to connect the DUT to the measurement system (Fig. 1).

Fig. 1. Simplified pulsed mode measurement setup

In this setup for a passive DUT the maximum open load output voltage is

$$V_{\text{DUT,max}} = V_0 \tag{1}$$

and the maximum short circuit DUT current is

$$I_{\text{DUT,max}} = \frac{V_0}{Z_0}.$$

(2)

The pulsed voltage source  $V_0$  and the characteristic impedance of the transmission lines  $Z_0$  limit the maximum DUT voltage and short circuit DUT current. To achieve higher level of  $V_{\rm DUT}$  and  $I_{\rm DUT}$ ,  $V_0$  can be increased and  $Z_0$  can be decreased.

Usually  $Z_0=50\,\Omega$  is widely used as a compromise between low loss and power handling capability for coaxial cables and measurement systems [1]. Example: in order to achieve 40 A short circuit DUT current in a  $Z_0=50\,\Omega$  system, a pulsed voltage source of 2 kV is required.

So far no commercial pulse generators based on solid-state devices or vacuum tubes are available to handle such high voltage with excellent pulse waveform quality with a dynamic range from below 1 V up to several kilo volts amplitude. The concept of using high voltage charged transmission lines to generate rectangular pulse waveforms with high quality is well known for a very long time, which has been described in [2] or even much earlier. This leads us to the classical transmission line pulse generator.

## II. THE TRANSMISSION LINE PULSE GENERATOR

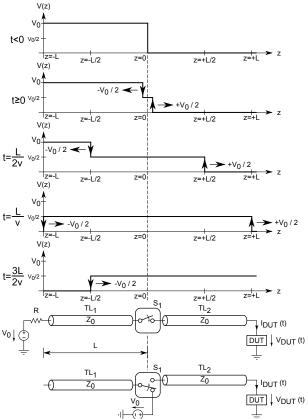

Fig. 2 shows the basic concept of the classical TLP generator. It consists of a high voltage source  $V_0$ , an impedance matched transmission line  $TL_1$ , the switch  $S_1$  and the transmission line  $TL_2$ . The necessary core

Fig. 2. The classical transmission line pulse (TLP) generator

elements are just two:  $TL_1$  and  $S_1$ . In the bottom of Fig. 2 two possible circuit realisations of the TLP generator are shown. Both are based on the basic principle of an open ended transmission line  $TL_1$  with a characteristic impedance  $Z_0$  and a mechanical length L.  $TL_1$  is often called charge line. For the initial condition at times t < 0,  $TL_1$  has to be charged with high voltage  $V_0$ . This can be done at the open end of  $TL_1$  using a resistor

$$R \gg Z_0$$

(3)

or directly at the switch side using a single pole, double throw switch (SP2T).  $\boldsymbol{v}$  is the propagation velocity in the transmission line

$$v \approx \frac{c}{\sqrt{\epsilon_r}}$$

(4)

with c the speed of light and  $\epsilon_r$  the relative dielectric constant of the transmission line inner insulator.  $v \approx 0.2 \text{ m/ns}$  is a good rule of thumb for polytetrafluoroethylene (PTFE or Teflon) dielectrics.

# A. How the Pulse is Generated

In the general case, the amplitude of the wave reflected at the open end of the charge line is determined by the reflection coefficient  $\rho$ . The value of  $\rho$  depends on the characteristic impedance  $Z_0$  and R, the termination resistance at the end of the line:

$$\rho = \frac{R - Z_0}{R + Z_0} \tag{5}$$

If R is very high or  $\infty$ , then  $\rho = +1$ . This means when a voltage wave hits the open end, the current has nowhere to go, and so a voltage wave of the same polarity propagates back up the line, adding to the original voltage. With this background we can consider the states along the charge line  $TL_1$  in Fig. 2:

t<0 This is the initial condition: the switch  $S_1$  is open and  $\mathrm{TL}_1$  is charged with the high voltage  $V_0$  constant over the length L.  $\mathrm{TL}_2$  has no voltage potential.

t=0  $S_1$  switched on: after short time t>0 the voltage at the switch drops down to  $Z_0 \cdot V_0/(Z_0+Z_0) = V_0/2$  because source impedance of  $\mathrm{TL}_1$  and load impedance of  $\mathrm{TL}_2$  is  $Z_0$ . At this time two voltage waves start immediately to propagate in opposite directions. One voltage wave with amplitude  $+V_0/2$  starts to propagate in positive z direction. Another voltage wave with amplitude  $-V_0/2$  starts to propagate in negative z direction, adding to the original voltage.

$t = \frac{L}{2v}$  At this time both voltage waves have propagated already a distance of  $z = \pm L/2$ .

$t=rac{L}{v}$  The voltage wave along negative z direction with amplitude  $-V_0/2$  hits the open end of  $TL_1$ . A voltage wave with same polarity propagates back up the line and adds to the original voltage  $-V_0/2+V_0/2=0$  which leads to cancellation.

$t=rac{3L}{2v}$  The cancellation voltage wave propagates back up the line and has reached z=-L/2. At the same time the other voltage wave with  $+V_0/2$  amplitude has reached the location z=3L/2 (not shown in Fig. 2).

This consideration leads to the conclusion that a rectangular pulse waveform is propagating along the transmission lines. On the transmission line a mechanical distance of 2L is travelled by the waveform and the pulse width in the time domain is

$$t_p = \frac{2L}{v} \approx \sqrt{\epsilon_r} \cdot \frac{2L}{c} \tag{6}$$

which is the basic design equation of the classical TLP generator.

# B. Challenges of Realisation

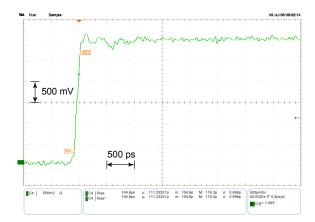

A usable pulse generator needs additional components for pulse shaping, reflection suppression and programmable parameter variation. The most challenging component is the switch  $S_1$ . State of the art is using a small mechanical reed switch with special gas filling, contact coating, sometimes mercury wetted, for high pulse waveform quality and reliability up to several kilo volts. Fig. 3 shows a typical pulse waveform rising edge, measured with a 12 GHz oscilloscope (Tektronix TDS6124C) at 40 GS/s sampling rate.

Fig. 3. TLP waveform measurement result at 40 GS/s [3]

### III. THE TLP MEASUREMENT SYSTEM

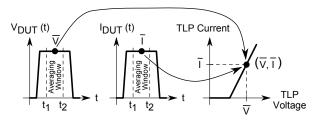

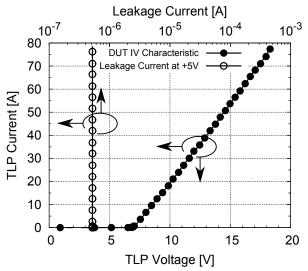

For the investigation and development of ESD protection devices T. Maloney and N. Khurana did introduce TLP in 1985 for the first time [4]. Barth Electronics introduced the first commercial TLP system in the mid-1990s including the concept and calibration of the measurement system [5], [6]. The DUT (Fig. 1) is excited with rectangular pulse waveforms with variable amplitude. The voltage waveforms  $V_{\mathrm{DUT}}(t)$  and current waveforms  $I_{DUT}(t)$  at the DUT are recorded using a digital high speed oscilloscope with single shot waveform capture capability. In general, the entire waveforms are valuable for the evaluation of the transient DUT characteristics in the time domain. Especially for ESD design the pulsed IV-characteristic, also called TLP-characteristic, is important (Fig. 4). Out of each captured voltage and current waveforms

Fig. 4. Extraction of the TLP characteristic

the arithmetic mean values  $\overline{V}$  and  $\overline{I}$  are calculated in the averaging window between  $t_1$  and  $t_2$ . For all pulse amplitudes these mean values are collected in an IV-diagram with the so called TLP voltage  $\overline{V}$  on the x-axis and the TLP-current  $\overline{I}$  on the y-axis. This diagram represents the quasi-stationary IV-characteristic of the DUT. It is always necessary to specify four important measurement conditions in addition to the diagram:

- 1) characteristic impedance of the TLP system

- 2) width of the pulse

- 3) rise time of the pulse

- 4) location of the averaging window:  $t_1$  and  $t_2$

Usually after the caption of each pulse waveform a dc leakage measurement is done and a second plot is

added to the TLP-characteristic: bottom x and left y axis remain as the traditional TLP voltage and current, and on top x and left y the evolution of leakage current (top x) versus TLP current (left y) is added [5], [6], as shown in Fig. 5.

Fig. 5. Measured TLP characteristic of a 5 V TVS diode

## A. Discrete Voltage and Current Sensors

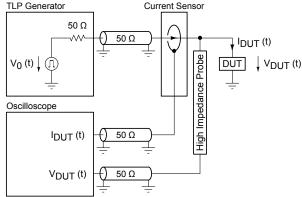

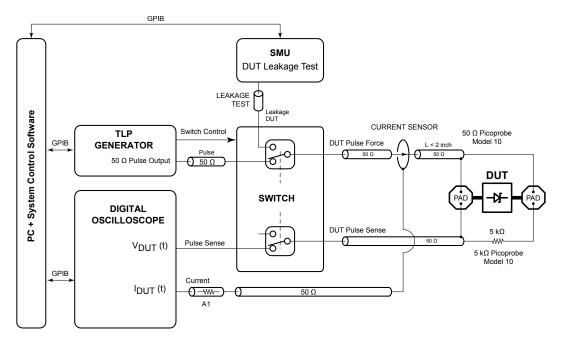

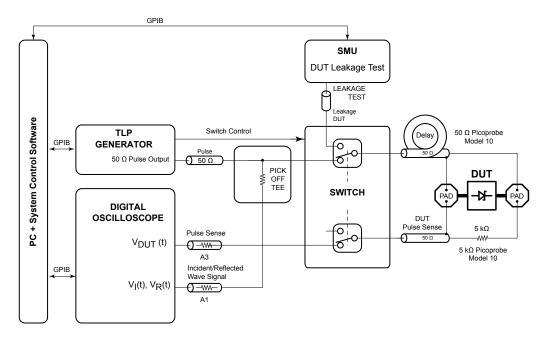

Fig. 6 shows a pulsed mode measurement setup with discrete sensors for current and voltage. The sensors should be located as close as possible to the DUT.

Fig. 6. Pulsed mode measurement setup with discrete sensors

Fig. 7. Discrete voltage and current sensors

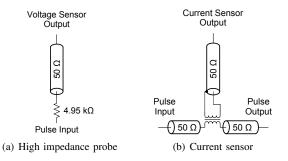

Fig. 7 show practical realisations for discrete voltage

and current probes. Voltage probes can be realised easier for higher bandwidth than current probes. The high impedance V-probe shown in Fig. 7(a) has an input impedance of 5 k $\Omega$  and a sensitivity (or voltage division ratio) of 50/(4950 + 50) = 0.01 V/V. The voltage sensor output must be terminated with 50  $\Omega$ . GGB [7] offers probe tips with such integrated resistors (Model 10) for wafer-level testing up to 11 GHz.

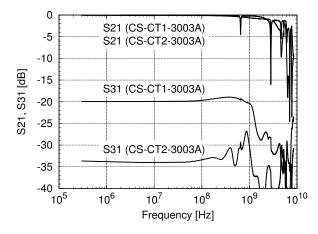

Discrete I-probes for pulse waveforms are often based on transformers, as shown in Fig. 7(b). The Tektronix CT-1 and CT-2 current sensors [8] have become an industry standard for TLP applications up to 100 A, depending on the pulse width  $t_p$ . However,

Fig. 8. Discrete 100 A current sensor with 50  $\Omega$  ports [3]

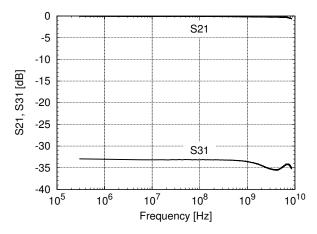

Fig. 9. Frequency response of discrete current sensors [3]

these sensors need to be enhanced with 50  $\Omega$  ports, as shown in Fig. 8. Fig. 9 shows the typical sensitivity versus frequency of the current sensors CS-CT1-3003A and CS-CT2-3003A [3] based on the Tektronix current sensors CT-1 and CT-2 [8]. The sensitivity in [V/A] can be evaluated from Fig. 9 by the calculation of  $10^{(S31/20)} \cdot 50$ .

Tab. I summarises the typical specifications of the Tektronix CT-1 and CT-2 current sensors. The maximum current depends on the pulse width and is limited by the L/R time constant and the amp x second rating. If the product (current x pulse width) exceeds the

Fig. 10. Simplified VF-TLP measurement setup

maximum rating, the core saturates and the output drops to zero.

| Sensor | Sensitivity<br>[V/A] | Bandwidth<br>[GHz] | Rise Time<br>[ns] | A x μs<br>Rating |

|--------|----------------------|--------------------|-------------------|------------------|

| CT-1   | 5                    | 1                  | < 0.35            | 1                |

| CT-2   | 1                    | 0.2                | < 0.5             | 50               |

TABLE I COMPARISON OF CURRENT SENSOR PARAMETERS [8]

# B. Remote Voltage and Current Sensing

The voltage  $V_{DUT}(t)$  and current  $I_{DUT}(t)$  can be calculated out from incident and reflected waves, far away from the DUT. This becomes indispensable if the pulse width becomes very small and the overlapping region of incident and reflected pulses is inadequate to take an I-V measurement directly at the DUT using discrete sensors. Usually this is the case at pulse width  $t_p \leq 10$  ns. The adequate measurement setup, shown in Fig. 10, is called very-fast TLP (VF-TLP) [9], [10] based on time-domain reflectometry (TDR).

The voltage probe (pickoff tee) is placed so far away from the DUT that incident and reflected waveforms appear separated. This can be achieved by inserting a delay line between the probes and DUT of mechanical length

$$L_D > \frac{t_p \cdot v}{2} \approx t_p \cdot \frac{c}{2\sqrt{\epsilon_r}}$$

(7)

With separated pulses the response at the DUT can be calculated by numerically overlapping the incident and reflected pulses according to following equations:

$$V_{\text{DUT}}(t) = V_I(t) + V_R(t) \tag{8}$$

$$I_{\text{DUT}}(t) = I_I(t) - I_R(t) \tag{9}$$

$V_I(t)$ ,  $V_R(t)$  are incident and reflected voltage waveforms.  $I_I(t)$ ,  $I_R(t)$  are incident and reflected current waveforms. Since incident and reflected pulses appear separate, there is a correlation between the current and voltage on the transmission line defined by its characteristic impedance  $Z_0$  according to:

$$I_I(t) = \frac{V_I(t)}{Z_0}$$

(10)

$I_R(t) = \frac{V_R(t)}{Z_0}$  (11)

$$I_R(t) = \frac{V_R(t)}{Z_0} \tag{11}$$

Fig. 11. Four point Kelvin TLP method including dc leakage measurement

By combining Eqn. 10, Eqn. 11 and Eqn. 9, the following equation is obtained

$$I_{\text{DUT}}(t) = \frac{V_I(t) - V_R(t)}{Z_0}$$

(12)

with  $Z_0 = 50~\Omega$ . Thus,  $V_I(t)$  and  $V_R(t)$  gives enough information to calculate  $V_{\rm DUT}(t)$  and  $I_{\rm DUT}(t)$ . In order to refine the results and to improve the accuracy, the frequency response of all components have to be included in the calculations by calibration and deembedding.

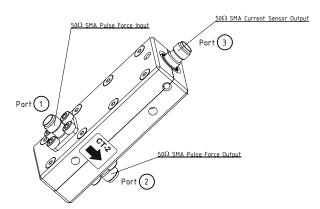

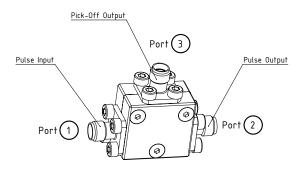

Fig. 12 shows a practical realisation of a pickoff-tee and the measured frequency response (Fig. 13).

Fig. 12. 3-port pickoff-tee [3]

#### C. Error Sources

In order to achieve high resolution and high accuracy in the time domain, proper compensation of the non-ideal characteristics of the components in the measurement system is required. Major contribution come from interconnection cables (lossy transmission lines), voltage probes, current sensors and parasitic contact resistance in case of wafer measurements with probes.

Fig. 13. Frequency response of a pickoff-tee [3]

# IV. MEASUREMENT TECHNIQUES

## A. Four Point Kelvin TLP Method

To eliminate the error from non-zero contact resistance at high currents, a four point Kelvin method is preferred to measure the differential voltage directly at the device (Fig. 11) [11].

On the pulse force line a standard 50  $\Omega$  ground-signal (GS) type RF probe tip is used. The discrete current sensor should be located as close as possible to the DUT, typically not more than 5 cm far away. Thus, the setup is suitable for pulse with of  $t_p > 5$  ns.

The sense probe tip has an integrated resistive divider, which enables the voltage to be measured with minimal parasitic loading (1-5 k $\Omega$ ). The bandwidth of the high impedance probe is 7 to 11 GHz depending on the probe tip model.

To ensure differential voltage measurement directly

Fig. 14. Four point Kelvin VF-TLP method including dc leakage measurement

at the device sheath waves should be suppressed on the transmission lines with ferrite cores and the ground of the probe tip holder should be isolated from the chuck and DUT fixture surrounding grounds.

The switch configuration with the source meter unit (SMU) is used to perform a dc (spot) leakage measurement in the pA to mA range after each high current pulse, in order to check if the DUT is already damaged or starts degrading. This method can be used for wafer-level as well as for component- or circuit level measurements.

# B. Four Point Kelvin VF-TLP Method

For VF-TLP measurements with pulse widths <10 ns, incident and reflected signals are recorded separately with a wide-band pickoff tee in the pulse-force line (see Fig. 14). The transient device response is calculated by combining the incident and reflected pulse signals numerically according Eqn. 8 (DUT voltage) and Eqn. 12 (DUT current).

But the DUT voltage is preferably measured directly with a second Picoprobe Model-10 with integrated voltage dividing resistor. This assures high bandwidth and minimizes the voltage error due to parasitic contact resistance. It also eliminates the digital noise that is typical for voltage measurements of low-ohmic devices with this method. In addition precise de-embedding of cable loss (amplitude and phase) enables accurate pulse measurements in the time-domain.

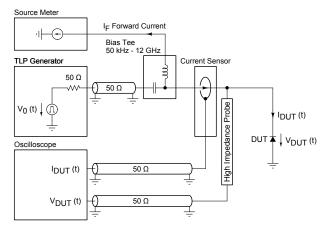

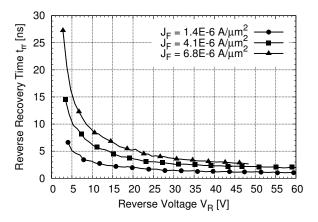

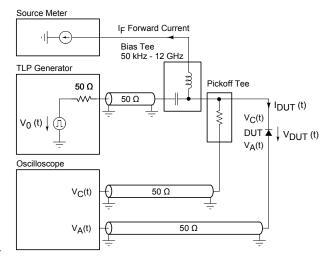

## C. Reverse Recovery Time of Diodes

Reverse recovery measurements are becoming more and more important to determine the ESD robustness of circuits during operation. The recovery times can be measured extremely fast and efficient with TLP in the range from about 200 ps up to 1 µs. The DUT

Fig. 15. 50  $\Omega$  reverse recovery measurement setup

is mounted in a 50  $\Omega$  test fixture. When a diode is conducting current in the forward direction, a significant amount of charge is injected into the resistivity region and the PN junction of the diode. When reverse voltage is applied the extraction of this charge leads to the reverse recovery phenomenon [12], [13].

A diode reveals an excessive transient forward voltage when it is switched rapidly into the forward conduction region. The amplitude and time duration of this voltage peak is representing the forward recovery characteristic [14].

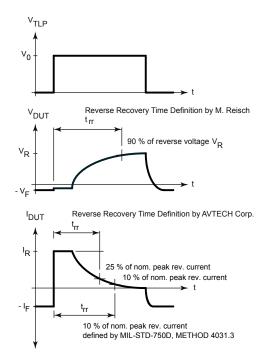

In the literature the reverse recovery time  $t_{rr}$  of diodes is defined multiple with different procedures of extraction (Fig. 16) and with different impedance conditions [15], [16], [13].

1) Reverse Recovery Definition - I: 25% of nominal peak reverse current achieved: This definition is used by commercial reverse recovery equipment manufacturers [15].

Fig. 16. Typical reverse recovery waveforms with setup Fig. 15

- 2) Reverse Recovery Definition II: 10% of nominal peak reverse current achieved: This definition is recommended by the standard MIL-STD-750D, method 4031.3 for diodes with  $t_{rr}$  < 6 ns [13].

- 3) Reverse Recovery Definition III: 90% of reverse voltage achieved: Michael Reisch propose in his book [16], Section 14.2.3, page 629, to use 90% settling time of the reverse voltage. This definition gives a more worst case value of the reverse recovery time.

- 4) Reverse Recovery Definition IV: reverse recovered charge: A more general approach to evaluate the reverse recovery phenomenon is to plot the reverse recovered charge versus rate of rise of reverse current for different values of forward bias current [12].

If we follow [15] or the MIL-STD we can extract the reverse recovery time as follows:

- Set the pulse parameters to minimum available rise time (e.g. 100 ps) and a pulse width which is approximately two to three times the expected reverse recovery time.

- Operate diode in forward mode with a defined forward bias current I<sub>F</sub>.

- Apply a reverse mode TLP pulse with a defined reverse voltage  $V_R = V_{TLP} |V_F|$ . The pulse width of the TLP has to be increased until the voltage  $V_R$  remains steady state.

- Measurement of the nominal peak reverse current.

- Extract 25 % (or 10 % according MIL-STD) of the nominal peak reverse current.

- The time where the current I<sub>DUT</sub> decreases down to 25% (or 10% according MIL-STD) of the nominal peak reverse current, is the reverse recovery time.

Fig. 15 shows the block diagram of a 50  $\Omega$  reverse recovery time measurement setup. The DUT is operated with 50  $\Omega$  source resistance. The DUT voltage and currents are measured with discrete sensors. Therefore the setup is useful for  $t_{TT} >$  several ns.

Fig. 17 shows a typical result of a silicon diode, measured with setup Fig. 15 and extraction of 25 % of the nominal peak reverse current. For each forward current density just only one TLP sweep is required. Postprocessing of the captured TLP waveforms has been done using Matlab [17].

Fig. 18 shows a 100  $\Omega$  reverse recovery measurement setup. In contrast to Fig. 15 no current sensor is necessary, because  $I_{\rm DUT}(t) = V_A(t)/50\,\Omega$ . The pickoff-tee is used to measure the voltage at the cathode  $V_C(t)$ . The interconnection between pickoff tee and the DUT results in a separation of incident and reflected waves. Therefore, the setup is useful for  $t_{TT} >$  several ns.

Fig. 17. Reverse recovery measurement result of a silicon diode

Fig. 18.  $\,$  100  $\Omega$  reverse recovery measurement setup

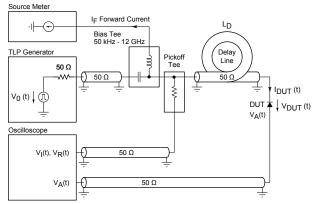

For extremely small recovery times in the sub-ns range the setup in Fig. 19 is based on TDR remote sensing. The DUT voltage and current can be calcu-

$100~\Omega$  recovery measurement setup with TDR

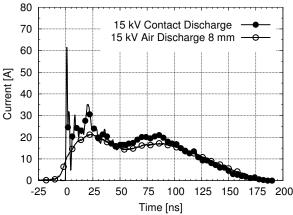

Fig. 20. Comparison of 15 kV contact and air discharge current.

lated as follows:

$$V_{\text{DUT}}(t) = V_I(t) + V_R(t) - V_A(t)$$

(13)

$$V_{\text{DUT}}(t) = V_I(t) + V_R(t) - V_A(t)$$

(13)

$I_{\text{DUT}}(t) = \frac{V_A(t)}{Z_0} = \frac{V_I(t) - V_R(t)}{Z_0}$  (14)

where  $Z_0 = 50 \Omega$ ,  $V_I(t)$  is the incident voltage wave,  $V_R(t)$  is the reflected voltage wave and  $V_A(t)$  is the voltage at the anode of the DUT.

#### V. ESD DESIGN

For packaging and handling ESD [18], TLP techniques up to 20 A have been used for the development of protection devices for more than 25 years. But recent developments are focused more on the development of system level ESD [19] protection solutions in two directions:

- 1) TLP characterisation of the ESD protection

- 2) TLP characterisation of the device/circuit/system to be protected

With this information the ESD protection solutions can be designed and optimized in a systematic way, in contrast to the widely used try-and-error approach in the past.

15 kV air discharge, according IEC-61000-4-2 [19], is a common standard for original equipment manufacturers (OEM) of e.g. mobile phones.

15 kV contact discharge is used by the component suppliers to guarantee the performance (clamping characteristic) and quality (minimum 1000 pulses to withstand at maximum ratings) of the ESD protection devices (Fig. 20).

The first peak current at 15 kV contact discharge exceeds 60 A. Thus, a TLP system with 80 A capabilities is suitable to develop 15 kV system level ESD protection solutions.

## VI. CONCLUSION

The characterisation in pulsed mode is heavily used in the development of semiconductor devices and circuits including ESD. Pulse generators are required which can deliver pulse waveforms up to several kilo volts in 50  $\Omega$ . The TLP generator is still state of the art in handling such high dynamic range.

The basic principle of the classical TLP generator has been reviewed. TLP measurement systems based on discrete voltage and current sensors, and the TDR based remote sensing (VF-TLP) method for measurements in the sub-ns range have been presented.

The four point Kelvin technique for TLP and VF-TLP is preferred for improved measurement accuracy at high currents.

Reverse recovery measurements are important to determine the ESD robustness of circuits during operation. Different measurement configurations, especially for the sub-ns region, are explained.

Finally, the necessity of an 80 A TLP generator was shown.

# REFERENCES

- [1] L. Espenschied and H. Affel, "U.S. Patent 1,835,031," December 8 1931.

- D. Bradley, J. Higgins, M. Key, and S. Majumdar, "A simple laser-triggered spark gap for kilovolt pulses of accurately variable timing," Opto-Electronics Letters, vol. 1, pp. 62-64, 1969

- (HPPI) Power Pulse Instruments [3] High http://www.hppi.de, 2009.

- [4] T. Maloney and N. Khurana, "Transmission line pulsing for circuit modeling of esd phenomena," in Proc. on EOS/ESD Symp., 1985, pp. 49-54.

- [5] J. Barth, K. Verhaege, L. Henry, and J. Richner, "Tlp calibration, correlation, standards, and new techniques," in Electrical Overstress/Electrostatic Discharge Symposium, 2000, pp. 85-

- -, "Tlp calibration, correlation, standards, and new tech-[6] niques," Electronics Packaging Manufacturing, vol. 24, no. 2, pp. 99-108, 2001.

- [7] GGB Industries, Inc., http://www.ggb.com/, 2012.

- Tektronix. Test and Measurement Equipment, http://www1.tek.com/, 2012

- [9] H. Gieser and M. Haunschild, "Very-fast transmission line pulsing of integrated structures and the charge device model,' in Proceedings of EOS/ESD Symposium, 1996.

- [10] E. Grund, "Deriving the DUT Current and Voltage Waveforms by Merging VF-TLP Incident and Reflected Signals,' EOS/ESD/EMI-Workshop, organized by M. Bafleur LAAS, Toulouse, F. 2006.

- [11] E. Grund and R. Gauthier, "TLP Systems with Combined 50 and 500-ohm Impedance Probes and Kelvin Probes," in proceedings of EOS/ESD Symposium, 2003, pp. 127–136.

- [12] N. Shammas, D. Chamund, and P. Taylor, "Forward and reverse recovery behaviour of diodes in power converter applications," in 24th International Conference on Microelectronics, vol. 1, 16-19 May 2004, pp. 3–10.

- [13] "MIL-STD-750D, method 4031.3, reverse recovery characteristics."

- [14] "MIL-STD-750D, method 4026.3, forward recovery voltage and time."

- [15] AVTECH Electrosystems LTD, "A comparison of reverse recovery measurement systems," Tech. Rep., November 2006.

- [16] M. Reisch, Elektronische Baulemente, 2nd ed. Springer, 2007.

- [17] MathWorks MATLAB and Simulink for Technical Computing, http://www.mathworks.com/, 2012.

- [18] ANSI/ESDA/JEDEC, "ESDA/JEDEC Joint Standard for Electrostatic Discharge Sensitivity Testing Human Body Model (HBM) Component Level," April 2012, http://www.jedec.org/.

- [19] International Electrotechnical Commission, "Electromagnetic compatibility (EMC) - Part 4-2: Testing and measurement techniques - Electrostatic discharge immunity test," 9th December 2008, ISBN 2-8318-1019-7, http://www.iec.ch/.